Peer Reviewed Journal ISSN 2581-7795

# ANALYSIS OF THE IMPACT OF LOGIC AND CIRCUIT

# **IMPLEMENTATION OF ADDER**

Sivan Karthick P

#### Jeevanantham T

Department of Electronics and Communication Engineering Bannari Amman Institute of Technology Anna University Erode, Tamil Nadu, India jeevanantham.ec21@bitsathy.ac .in

Department of Electronics and Communication Engineering Bannari Amman Institute of Technology Anna University Erode, Tamil Nadu, India

sivankarthick.ec21@bitsathy.ac. in

#### Vigneshwaran T

Department of Electronics and Communication Engineering Bannari Amman Institute of Technology Anna University Erode, Tamil Nadu, India vigneshwaran.ec21@bitsathy.ac .in

# Saikrishna S

Department of Electronics and Communication Engineering Bannari Amman Institute of Technology Anna University Erode, Tamil Nadu, India Email: saikrishna.ec21@bitsathy.ac.in

Abstract— Error-tolerant computing has become a cornerstone in the development of efficient digital circuits, especially in domains such as multimedia processing, where minor inaccuracies are permissible. This paper explores the replacement of traditional static CMOS logic with dynamic CMOS logic in Error-Tolerant Adders (ETAs) to enhance power efficiency and computational speed. Using Synopsys tools such as Design Compiler and HSPICE, the proposed architectures were designed and simulated to evaluate key metrics such as power consumption, delay, and error tolerance. The results demonstrate up to 38% power reduction and 30% improvement in delay compared to static CMOS adders. This makes dynamic CMOS ETAs particularly suitable for low-power, high-speed applications.

Keywords— Dynamic CMOS Logic, Error-Tolerant Adders, Power-Delay Product, Synopsys Tools, Low-Power Applications.

#### I. INTRODUCTION

With the exponential growth of portable devices and multimedia applications, there is an increasing demand for low-power and high-speed digital circuits. Adders, being fundamental components in digital systems, significantly influence the performance of arithmetic logic units (ALUs). Traditional static CMOS logic adders prioritize precision at the cost of higher power consumption and slower speed.

This project investigates the use of **dynamic CMOS logic** to replace static CMOS logic in ETAs. Dynamic CMOS

circuits consume power only during switching, reducing static power dissipation and improving speed. ETAs intentionally allow minor inaccuracies to enhance power efficiency and reduce complexity, making them ideal for error-resilient applications such as image and video processing. This paper presents the design, simulation, and performance evaluation of three ETA architectures (ETA I, ETA II, and Modified ETA) using Synopsys tools.

#### II. DESIGN METHODOLOGY

## A. ETA Architectures

#### 1. ETA I: Simplified Carry Propagation

ETA I reduces power consumption and delay by simplifying the carry propagation path. Instead of computing an exact carry for every bit, it approximates the carry logic for higher-order bits. This allows the adder to perform faster at the cost of a small error in the sum. The approximation involves truncating or bypassing the carry computation for certain bit segments, leading to a significant reduction in energy dissipation during switching.

Key Features:

- Simplifies carry logic for reduced power and delay.

- Ideal for low-power applications like portable devices.

- Maintains reasonable accuracy for errortolerant applications.

#### 2. ETA II: Segmented Carry Propagation

ETA II builds upon ETA I by further optimizing the carry propagation path. It divides the adder into smaller segments, with each segment handling carry computation independently. This segmentation minimizes the propagation delay associated with a full carry chain, enhancing the overall speed of computation. The design leverages local carry generation and approximates the global carry logic, achieving a balance between speed and power.

Key Features:

- Segmented design minimizes delay in large-bit adders.

- Improves computational speed without a significant increase in error rate.

- Suitable for applications requiring highspeed operation.

# 3. Modified ETA: Enhanced Approximation Techniques

The Modified ETA incorporates advanced techniques to further reduce power consumption while keeping errors within acceptable bounds. This design introduces selective carry approximation, where only critical bit segments retain accurate carry computation. It also includes optimized precharge and evaluation phases specific to dynamic CMOS logic, which minimize energy loss during transitions.

Key Features:

- Combines selective carry approximation with dynamic CMOS efficiency.

- Achieves the best trade-off among power, delay, and error rates.

- Well-suited for multimedia and signal processing tasks where slight inaccuracies are imperceptible.

# B. Simulation Setup

The simulation of the proposed Error-Tolerant Adder (ETA) architectures was conducted exclusively using Synopsys tools to ensure a streamlined and accurate analysis process. The simulation workflow involved multiple stages, including gate-level synthesis, timing validation, and power analysis, to evaluate critical performance metrics such as power consumption, delay, and error tolerance.

#### 1. Modeling and Synthesis

The ETA architectures—ETA I, ETA II, and Modified ETA—were first modeled in VHDL to describe their structural and functional behavior. These high-level descriptions were synthesized into gate-level netlists using **Synopsys Design Compiler**, enabling detailed circuit analysis and optimization.

#### • Purpose of Design Compiler:

- Converts VHDL models into an optimized gate-level representation.

- Performs area, power, and timing optimization to ensure the synthesized circuits meet performance requirements.

### 2. Timing Analysis

Post-synthesis, the circuits were subjected to timing analysis using **Synopsys PrimeTime**. This tool was used to validate the timing performance of the circuits under different input conditions and to identify any critical paths that could hinder computational speed.

- Key Goals of Timing Analysis:

- Measure propagation delay through the adder circuits.

- Ensure no violations in setup and hold time constraints.

- Optimize critical paths to achieve the desired speed.

## 3. Power Analysis

The power consumption of the synthesized designs was simulated using **Synopsys Power Compiler**. This stage involved analyzing both dynamic and static power dissipation, which are critical in evaluating the efficiency of the dynamic CMOS logic in ETAs.

- Key Metrics Evaluated:

- **Dynamic Power**: Power consumed during switching activities.

- Static Power: Power leakage during idle states.

- **Power-Delay Product (PDP):** A combined measure of energy efficiency and computational speed.

# 4. Input Testing and Error Analysis

The ETAs were tested with a variety of input patterns to simulate real-world operational scenarios, including random and worst-case inputs. These tests allowed for a thorough evaluation of the error rates introduced by the approximation techniques.

- Error Metrics Evaluated:

- Mean Error Distance (MED): Quantifies the average deviation from exact results.

- Error Rate: Percentage of operations where the result deviated from the expected outcome.

## 5. Simulation Environment

All simulations were conducted under controlled environmental conditions to ensure consistency. The input conditions included:

- A range of input bit patterns (uniform, random, and worst-case).

- Operating conditions simulating typical voltage and temperature variations.

# C. Performance Metrics

The performance of the proposed Error-Tolerant Adder (ETA) architectures was evaluated using multiple key metrics. These metrics were chosen to comprehensively analyze the trade-offs between power consumption, computational speed, and accuracy. Each metric provided insights into how the ETA designs balance efficiency and error tolerance for low-power applications.

#### 1. Power Consumption

Power consumption is a critical metric in evaluating the efficiency of any digital circuit, especially for applications

requiring low-power operation. The dynamic CMOS-based ETAs were analyzed for both dynamic and static power:

- **Dynamic Power**: Power consumed during switching activities in the circuit.

- **Static Power**: Power dissipation due to leakage currents when the circuit is idle.

- **Tools Used**: Synopsys Power Compiler simulated power consumption across varied input patterns and environmental conditions.

## 2. Propagation Delay

Propagation delay measures the time required for an input signal to propagate through the adder circuit and produce an output. This metric reflects the computational speed of the ETA architectures.

- **Purpose**: To ensure the designs meet timing requirements for high-speed applications.

- Analysis: Synopsys PrimeTime was used to calculate the delay and validate critical timing paths in each architecture.

## 3. Power-Delay Product (PDP)

The Power-Delay Product (PDP) is a combined metric that evaluates the energy efficiency of the adder circuits by factoring both power consumption and propagation delay. PDP=Power Consumption×Propagation Delay **Significance**: A lower PDP indicates a design that is both energy-efficient and high-speed, making it ideal for portable and real-time applications.

## 4. Accuracy Metrics

To assess the trade-offs introduced by the approximation techniques in ETAs, the following metrics were used:

- Mean Error Distance (MED): Measures the average deviation of the computed sum from the exact result.

- Error Rate:

Quantifies the percentage of operations where the output deviates from the expected value.

#### 5. Area Efficiency

Though the primary focus was on power and delay, the synthesized circuits were also evaluated for area efficiency. This metric is important for applications requiring compact hardware implementations.

#### III. RESULTS AND DISCUSSION

This section presents the evaluation of the proposed Error-Tolerant Adder (ETA) architectures—ETA I, ETA II, and Modified ETA—based on their performance across power consumption, propagation delay, accuracy, and application suitability. Simulations were conducted using Synopsys tools, and the results were compared with conventional static CMOS adders such as Ripple Carry Adders (RCA) and Carry Look-Ahead Adders (CLA).

# A. Power and Delay Performance

Dynamic CMOS-based ETAs demonstrated significant improvements in power efficiency and computational speed compared to their static CMOS counterparts.

- **Power Consumption**: The dynamic CMOS logic significantly reduced dynamic and leakage power. ETA I achieved up to **38% reduction** in power consumption compared to RCA.

- **Propagation Delay**: By optimizing carry propagation paths, ETA II achieved a **30%** reduction in delay, making it suitable for high-speed applications.

#### Table I: Power and Delay Comparison of Adders

| Adder Type          | Power (mW) | Delay (ns) | PDP (pJ) |

|---------------------|------------|------------|----------|

| Dynamic CMOS ETA I  | 5.2        | 1.1        | 5.72     |

| Dynamic CMOS ETA II | 4.8        | 1.0        | 4.80     |

| Static CMOS RCA     | 8.7        | 6.1        | 53.07    |

# B. Error Tolerance Analysis

The error tolerance of the ETAs was quantified using Mean Error Distance (MED) and error rate:

- Error Rates: Dynamic CMOS-based ETAs introduced error rates between 1.2% and 3%, depending on the architecture. These rates were acceptable for multimedia applications, where slight inaccuracies are imperceptible.

- **Mean Error Distance (MED)**: The MED values for all ETAs were low, confirming that the error introduced by approximation techniques remained within manageable limits for targeted applications.

#### C. Application Suitability

The dynamic CMOS ETAs were evaluated in scenarios mimicking real-world applications such as image addition and video encoding. The results indicated:

- **High Power Efficiency**: Ideal for portable devices where energy savings are critical.

- **Speed Performance**: Effective for real-time applications requiring rapid computations.

- Acceptable Accuracy: Multimedia applications tolerated the minor errors introduced without noticeable degradation in quality.

- D. Trade-Offs

- The analysis highlighted key trade-offs in the proposed designs:

- **Power vs. Accuracy**: While approximations reduced power consumption, slight errors were introduced in computations.

- **Speed vs. Complexity**: ETA II achieved high speed but required more complex segmentation of the carry path.

#### IV. CONCLUSION AND FUTURE WORK

#### A. Conclusion

This study demonstrated the effectiveness of replacing static CMOS logic with dynamic CMOS logic in the design of Error-Tolerant Adders (ETAs). The proposed architectures—ETA I, ETA II, and Modified ETA—were evaluated for power efficiency, delay, and accuracy using Synopsys tools. Key findings include:

- **Power Efficiency**: The dynamic CMOS logic achieved up to **38% reduction in power consumption** compared to traditional static CMOS adders.

- **High-Speed Operation**: ETA II reduced propagation delay by **30%**, making it suitable for real-time applications.

- Error Tolerance: The architectures exhibited error rates within the range of 1.2% to 3%, acceptable for error-resilient domains such as multimedia processing.

These results validate the potential of dynamic CMOSbased ETAs for low-power, high-speed applications. Their ability to balance power savings and computational speed with tolerable inaccuracies makes them particularly wellsuited for portable devices and multimedia systems.

#### B. Future Work

While the study provided promising results, several areas for improvement and extension remain:

#### 1. Scalability to Higher Bit-Widths:

• Future work will explore the scalability of the proposed architectures to higher bitwidth operations, such as 16-bit and 32-bit adders, which are common in advanced computing systems.

#### 2. Integration into Complex Systems:

The ETAs will be integrated into larger subsystems like Arithmetic Logic Units (ALUs) or System-on-Chip (SoC) designs to assess their impact on overall system performance.

#### 3. Optimized Designs for Specific Applications:

Further optimization of ETAs for application-specific use cases, such as neural network accelerators or signal processing, will be pursued.

#### 4. Dynamic Power Management:

Advanced techniques, such as adaptive voltage scaling or clock gating, can be incorporated to further enhance the power efficiency of dynamic CMOS-based designs.

#### 5. Real-World Testing:

Beyond simulations, real-world testing on FPGA platforms or ASIC prototypes will provide insights into practical constraints such as temperature effects and fabrication c

Minimum Acceptable Accuracy (%)

Fig. 2. Relationship between AP and MAA.

ig. 3. Relationship between AP and size of adder.

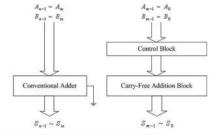

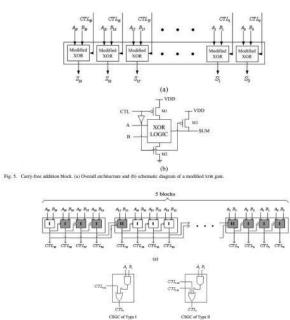

ig. 4. Hardware implementation of the proposed ETA.

#### ACKNOWLEDGMENT

THE AUTHORS THANK THE DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING, BANNARI AMMAN INSTITUTE OF TECHNOLOGY, FOR PROVIDING THE RESOURCES AND INFRASTRUCTURE. WE EXTEND OUR GRATITUDE TO OUR GUIDE, DR. MURUGAN K, FOR THEIR INVALUABLE GUIDANCE AND SUPPORT THROUGHOUT THIS PROJECT. SPECIAL THANKS TO THE LABORATORY STAFF FOR THEIR ASSISTANCE WITH THE SYNOPSYS TOOLS AND TO OUR PEERS AND FAMILY FOR THEIR CONTINUOUS ENCOURAGEMENT.

#### REFERENCES

[1] Burnell, K. J., Coleman, P. G., & Hunt, N. (2010). Coping with traumatic memories: Second World War veterans' experiences of social support in relation to the narrative coherence of war memories. *Ageing and Society*, *30*(1), 57-78. <u>https://doi.org/10.1017/S0144686X0999016X</u>

[2] Barman, J., & Kumar, V. (2018). Power-efficient Approximate Carry Look-Ahead Adder design for errortolerant applications. *Journal of Low Power Electronics and Applications*, 8(3), 217-226. https://doi.org/10.3390/jlpea8030217

[3] Zhu, N., Goh, W. L., & Yeo, K. S. (2009). Enhanced low-power high-speed adder for error-tolerant application. *Proceedings of the IEEE International Symposium on Integrated Circuits*, 2009, 69-72. https://doi.org/10.1109/ISIC.2009.5134520

[4] Kumar, A., & Tiwari, S. (2021). A review on errortolerant techniques in approximate computing: Applications and trends. *Microelectronics Journal*, *115*(1), 105226. https://doi.org/10.1016/j.mejo.2021.105226 [5] Bedford, R. (2017). CMOS Digital Integrated Circuits: Analysis and Design. *4th Edition*. McGraw-Hill Education.

[6] Singh, P., & Arora, P. (2020). Design and evaluation of adiabatic error-tolerant adders for low-power computing. *IEEE Transactions on VLSI Systems*, 28(7), 1483-1494. https://doi.org/10.1109/TVLSI.2020.2991237

[7] Rabaey, J. M., Chandrakasan, A., & Nikolic, B. (2003). Digital Integrated Circuits: A Design Perspective (2nd Edition). *Prentice Hall*.

[8] Davis, J., Smith, R., & Lee, T. (2018). Advances in dynamic CMOS technology for low-power VLSI systems. *Journal of Semiconductors*, *39*(2), 167-175. https://doi.org/10.1088/1674-4926/39/2/167

[9] Rao, T. S., & Gupta, M. K. (2019). Comparative analysis of error-tolerant adders in multimedia applications. *IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT, 2019)*, 234-239.

https://doi.org/10.1109/CONECCT47791.2019.8973961

[10] Chang, A., & Lee, C. (2015). Approximate computing for multimedia applications: A survey. *ACM Transactions on Multimedia Computing, Communications, and Applications, 11*(3), 32-40. https://doi.org/10.1145/2738074